World Journal of Engineering Research and Technology

<u>WJERT</u>

www.wjert.org

SJIF Impact Factor: 4.326

# A NOVEL APPROACH FOR DIAGNOSIS OF FAULTS IN ANALOG VLSI CIRCUITS BY THE APPLICATION OF DISCRETE METHOD

Baldev Raj\*<sup>1</sup> G. M. Bhat<sup>2</sup>

<sup>1</sup>Department of Electronics and Communication Govt. College of Engineering and Technology Jammu.

<sup>2</sup>Institute of Engineering and Technology Safapora, USIC University of Kashmir.

Article Received on 19/09/2017 Article Revised on 10/10/2017 Article Accepted on 31/10/2017

\*Corresponding Author Baldev Raj Department of Electronics and Communication Govt. College of Engineering and Technology Jammu.

### ABSTRACT

Analog circuit testing is one of difficult task, due mainly the lack of fault models and accessibility to internal nodes. An approach is presented for analog circuit modeling and testing to overcome this problem In this paper we proposed a method to detect faults in analog VLSI circuits using discrete method. The area of fault modelling in

analog VLSI circuit does not achieve the same degree as compare to digital fault model. So there is need of simple analog fault model which works effectively. As we need more application on one chip the circuitry of analog VLSI circuit becomes more complicated so it is very difficult to analyses fault in that circuit. In this method we use discretization technique and also apply bilinear transformation. Our method is simple and not time consuming as compare to other methods. The all simulation and algorithm are made with the help of MATLAB/Simulink.

KEYWORDS: Parametric faults, analog VLSI circuits, discrete, Filter.

#### **INTRODUCTION**

In present scenario analog VLSI circuits are used in wide number of application such as multimedia, cellular communication, digital signal processing and data acquisition. The testing of analog VLSI circuit is a major task before designing and fabrication of any product. The fault detection in analog VLSI circuits is very difficult task due to complexity nature of analog circuits. There is no simple fault model for analog VLSI circuits as present in digital

circuits. There are two types of fault model are present in analog circuits. These are catastrophic fault model and parametric fault model. In catastrophic, there is large deviation at output due to large variation in component values (due to short or open circuit).

In parametric, the component value will change from nominal value to certain extent. The parametric fault cause due to change in component value due time and environment. The parametric fault sometimes causes the change in output behavior of system sometimes not. But catastrophic fault change the behavior of circuit completely. The testing of analog circuits consume 30% of total manufacturing cost of product.<sup>[1]</sup> The cost occur in analog circuits testing due to functional testing techniques, these require large number of measurements for test. In this paper we present a analog fault detector using discretization.<sup>[2,3,4,5]</sup>

#### **Basic Principle**

A large number of analog VLSI circuits can be represented by linear state variable equations.<sup>[6,7,8]</sup> For simplicity here we take single output state variable circuit where the output of every block contain a capacitor (memory element.).The state equation for the circuit is given by

$$\dot{X}(t) = A X(t) + B U(t)$$

$$X(t) = [x_1(t), x_2(t), \dots, x_n(t)]^T$$

is state vector containing n variable.

$$\dot{X}(t) = [\dot{x}_1(t) + \dot{x}_2(t), \dots, \dot{x}_n(t)]^T$$

(1)

Here  $\dot{x_1}(t)$  is derivative with time. The output of the system is given by y (t). y(t) = C X(t) + D U(t) (2)

By taking Laplace transform we change state variable equation from time domain to frequency s domain that is given by

$$sX(s) = A X(s) + BU(s)$$

<sup>(3)</sup>

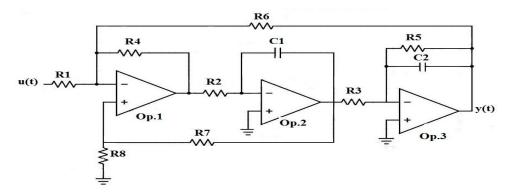

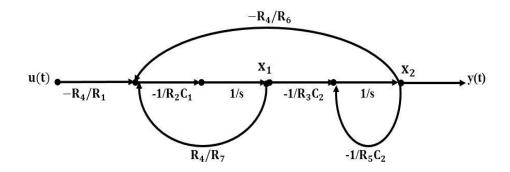

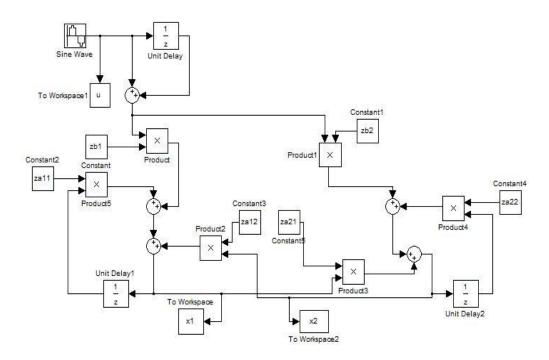

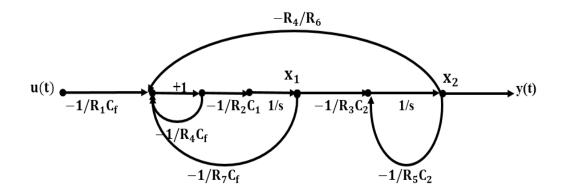

From these equation we can derive from signal flow graph.<sup>[9,10]</sup> Here we taking example of Biquadratic Filter circuit. In Fig 1. And Fig 2. Shown the circuit diagram and signal flow graph of biquadratic filter circuit. The biquadratic filter circuits contain three op-amp. First operational amplifier is inverting op-amp, second is integrator and third is lossy integrator.

Figure 1: Circuit Diagram of Biquadratic filter.

Figure 2: Signal flow graph of Biquadratic filter circuit.

By using all the resistor value equal to R and all capacitor value equal to C. then we have  $\omega_0 = 1/RC$ . From Fig. 2 we can write state equation

$$\begin{bmatrix} x_1(s) \\ x_2(s) \end{bmatrix} = \begin{bmatrix} -\omega_0 & \omega_0 \\ -\omega_0 & -\omega_0 \end{bmatrix} \begin{bmatrix} \frac{x_1(s)}{s} \\ \frac{x_2(s)}{s} \end{bmatrix} \begin{bmatrix} \omega_0 \\ 0 \end{bmatrix} u(s)$$

(4)

By applying bilinear transform we get z transform from s domain. In bilinear transform

$$s = \frac{t^2 t^2}{t_s z + 1} \tag{5}$$

Here  $t_s$  is sampling time.

By using equation (4) and (5) we get

$$Z_A = (2/t_s I - A)^{-1} (2/t_s I + A)$$

(6)

$$Z_B = (2/t_s I - A)^{-1}B$$

(7)

So that we can write

$$X(z) = Z_A z^{-1} X(z) + Z_B z^{-1} (u(z) + u(z))$$

(8)

Here  $z^{-1}$  is delay. This equation can be write in time domain

$$X(t_k) = Z_A X(t_{k-1}) + Z_B(u(t_{k-1}) + u(t_k))$$

(9)

Here u(t) is input for simulation of biquadratic filter circuit. And sampling rate is  $1/t_s$ . And sampling frequency is.  $f(s) = 1/t_s$ .

In biquadratic filter circuit by using R=10k and C=0.02 $\mu$ F and by using this we get  $\omega_0 = 5000 Hz$  and using nyquist criterion  $t_s$ =0.0001sec.By using these parameter we find state equation in Z domain.

$$\begin{bmatrix} x_1(z) \\ x_2(z) \end{bmatrix} = \begin{bmatrix} 0.538 & 0.308 \\ -0.308 & -0.538 \end{bmatrix} \begin{bmatrix} z^{-1} \cdot x_1(z) \\ z^{-1} \cdot x_2(z) \end{bmatrix} + \begin{bmatrix} 0.192 \\ -0.038 \end{bmatrix} (u(z) + z^{-1} \cdot u(z))$$

(10)

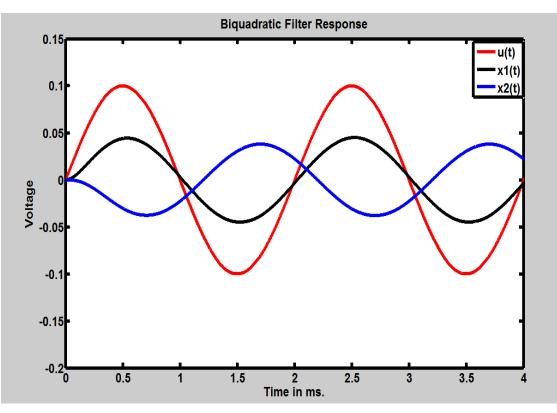

By applying sinusoidal input u (t)=0.1sin( $2\pi$ .500t). We simulate biquadratic filter circuit.

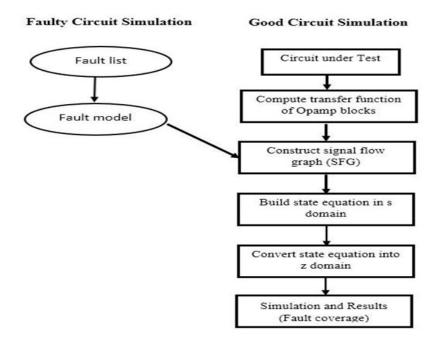

#### Algorithm for fault diagnosis

The algorithm for fault modeling and detection is constructed with the help of MATLAB and Simulink.<sup>[9]</sup> The entire algorithm to compute fault in circuits is shown in Fig. 8. With the help of given algorithm we can easily detect the fault in analog VLSI circuit. In this paper we applied our algorithm to two circuits first is Biquadratic filter circuit and second circuit is leap frog filter circuit both circuit are benchmark circuit. Before the implementation of testing method, the method should be applicable to this circuit.<sup>[10,11]</sup>

Figure 3: Algorithm used for fault simulation.

## **Modeling of Faults**

For the measurement of different fault occur in circuit one should have complete fault list. There are two types of faults occur in analog VLSI circuits. These are parametric fault and catastrophic fault.<sup>[12]</sup>

Parametric faults occur in circuit due to some manufacturing defects (change in some parameter like due to doping level and due to oxide thickness). Due to parametric faults in circuit the tolerance of component will vary to certain value. In these types of faults the circuit output may or may not be changed. Because the value of component is increase or decrease to certain value.<sup>[13]</sup>

These type of fault we can remove with the help of knowing the tolerance of component (ie. If there is some change in value then how much output of system is changed).Catastrophic faults are completely changed the output of the circuit. These cause the short circuit or open circuit. These are also called hard fault. Due to these type of fault the behavior of system changed drastically.<sup>[14,15]</sup> These are random faults.

Figure 4: Biquadratic Filter simulation using MATLAB.

Figure 5: Biquadratic filter in discrete form (using Simulink).

#### 5. Effect Cause by Single Fault in Circuit

When we simulate the circuit with fault the z domain state equation is assumed as discrete network as shown in Fig. 5. Here the coefficient of multiplier are  $za_{ij}$  and  $zb_i$ . These are the elements from  $Z_A$  and  $Z_B$ .Single fault is appears as with multiple faults in discrete circuit.<sup>[16,17]</sup> For example there is fault in  $R_5$ . That is the value of  $R_5$  is changed from its original value. The original value of  $R_5$ =10k and due to fault the value is change to  $R_5$ =1k. This fault effect the entire matrices of s domain where  $R_5$  is present. Where as it effects both in z domain that is  $Z_A$  and  $Z_B$ . The change in state equation due to fault occur in circuit

$$\begin{bmatrix} x_1(s) \\ x_2(s) \end{bmatrix} = \begin{bmatrix} -5000 & 5000 \\ -5000 & -500 \end{bmatrix} \begin{bmatrix} x_1(s)/s \\ x_2(s)/s \end{bmatrix} + \begin{bmatrix} 5000 \\ 0 \end{bmatrix} u(s)$$

By in z domain it is given as

$$\begin{bmatrix} x_1(z) \\ x_2(z) \end{bmatrix} = \begin{bmatrix} 0.526 & 0.372 \\ -0.372 & -0.860 \end{bmatrix} \begin{bmatrix} z^{-1} \cdot x_1(z) \\ z^{-1} \cdot x_2(z) \end{bmatrix} + \begin{bmatrix} 0.191 \\ -0.047 \end{bmatrix} (u(z) + z^{-1} \cdot u(z))$$

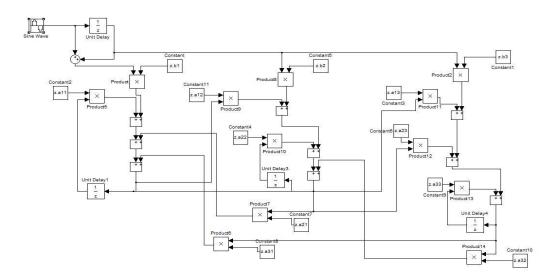

Number of states changed due to single fault in circuit. The major cause of circuit failure is parasitic capacitance. For example here we consider capacitance  $C_f$  effect which is at negative terminal of operational amplifier first and output terminal of operational amplifier.<sup>[18]</sup> Due to this capacitance faulty state is generated which will increase the states. Here we represent it as faulty state ( $x_f$ ). The fig. 6shows the signal flow graph with increased states due to faults

#### Figure 6: Signal flow graph with increased states

Due to the presence of presence of parasitic capcitance the state equation is also changed and can be written as.

$$\begin{bmatrix} x_1(s) \\ x_2(s) \\ x_3(s) \end{bmatrix} = \begin{bmatrix} 0 & 0 & -5000 \\ -5000 & -5000 & 0 \\ 5000 & -5000 & -5000 \end{bmatrix} \begin{bmatrix} x_1(s)/s \\ x_2(s)/s \\ x_3(s)/s \end{bmatrix} + \begin{bmatrix} 0 \\ 0 \\ 5000 \end{bmatrix} u(s)$$

And in z domain are given below

$$\begin{bmatrix} x_1(z) \\ x_2(z) \\ x_f(z) \end{bmatrix} = \begin{bmatrix} 0.887 & 0.075 & -0.377 \\ -0.377 & -0.585 & 0.075 \\ 0.453 & -0.302 & 0.509 \end{bmatrix} \begin{bmatrix} z^{-1} \cdot x_1(z) \\ z^{-1} \cdot x_2(z) \end{bmatrix} + \begin{bmatrix} 0.047 \\ -0.009 \\ -0.189 \end{bmatrix} (u(z) + z^{-1} \cdot u(z))$$

Figure 7: Discrete model with increased state due to fault (using Simulink).

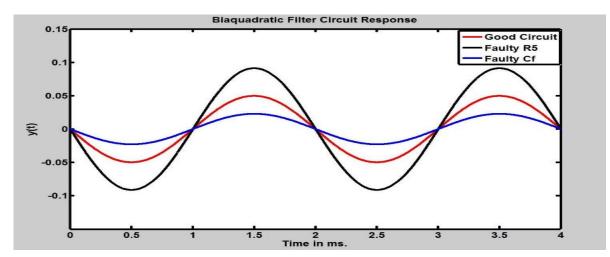

Fig. 7 shows Simulink model for increased states by faults. By simulation of above model we plot biquadratic filter response, which is shown in fig.8

Figure 8: Response of Biquadratic filter at f=500Hz.

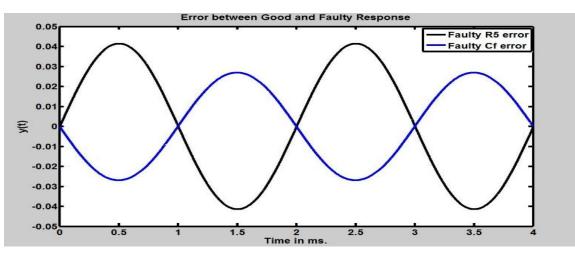

Figure 9: Error between the good and faulty response of Biquadratic filter circuit

# **RESULTS AND DISCUSSION**

Our approach work serially for analog VLSI not like parallel approaches. Because it is not possible to detected all the faults in the circuit. Here we apply this approach to the parametric fault occur in the analog VLSI circuit that is if the value of the component is changes slightly then the output response of the circuit is changed completely. So it is very necessary to detect this fault. Here in first case we assume fault in  $R_5$  resistor in the biquadratic filter.<sup>[19]</sup>

Then with the help of our approach we detect the response of the good and faulty biquadratic filter circuit. This approach is applicable to all types of circuit which we can convert into the signal flow graph.<sup>[20]</sup>

Our approach is simple and efficient approach as compare to the methods used now a days. In this paper fault simulation is done on two benchmark circuit. In first circuit we consider two parametric fault in biquadratic filter circuit where as in second circuit contain only one parametric fault in Leapfrog filter circuit, both the filter are simulate at different frequency that is 500Hz and 1kHz for biquadratic filter and 1kHz for leapfrog filter circuit.

Figure 7 show the response of biquadratic filter circuit that is we use our algorithm to detect the parametric fault occur in circuit. This figure shows that the circuit response is complete changed due to the presence of parametric faults in the circuit .Second filter leapfrog filter is simulated with the help of our approach by assuming the fault in R2 resistor.in this case we also assume the parametric fault in circuit. And by simulation of algorithm at 1kHz, we detect fault in circuit. The table 1 shows the result for biaqudratic filter circuit.

| Sr. No. | Component             | Original Value | Faulty Value | Testing Freq.<br>(Hz) | Result |

|---------|-----------------------|----------------|--------------|-----------------------|--------|

| 1.      | R1                    | 10K            | 15K          | 1.00e <sup>+02</sup>  | Y      |

| 2.      | R1                    | 10K            | 5K           | 1.00e <sup>+02</sup>  | Y      |

| 3.      | R <sub>2</sub>        | 10K            | 15K          | 1.00e <sup>+03</sup>  | N      |

| 4.      | R <sub>2</sub>        | 10K            | 5K           | 1.00e <sup>+03</sup>  | Ν      |

| 5.      | R <sub>3</sub>        | 10K            | 15K          | 1.00e <sup>+03</sup>  | Y      |

| 6.      | R <sub>3</sub>        | 10K            | 5K           | 1.00e <sup>+03</sup>  | Y      |

| 7.      | R <sub>4</sub>        | 10K            | 15K          | 1.00e <sup>+03</sup>  | N      |

| 8.      | R <sub>4</sub>        | 10K            | 5K           | 1.00e <sup>+03</sup>  | Y      |

| 9.      | R <sub>5</sub>        | 10K            | 15K          | 1.00e <sup>+03</sup>  | Y      |

| 10.     | R <sub>5</sub>        | 10K            | 5K           | 1.00e <sup>+03</sup>  | Y      |

| 11.     | R <sub>6</sub>        | 10K            | 15K          | 1.00e <sup>+03</sup>  | Y      |

| 12.     | R <sub>6</sub>        | 10K            | 5K           | 1.00e <sup>+03</sup>  | Y      |

| 13.     | <i>C</i> 1            | 0.01µF         | 0.02 µF      | 1.00e <sup>+03</sup>  | N      |

| 14.     | <i>C</i> 1            | 0.01µF         | 0.005 µF     | 1.00e <sup>+03</sup>  | N      |

| 15      | <i>C</i> <sub>2</sub> | 0.01µF         | 0.02 µF      | 1.00e <sup>+03</sup>  | N      |

| 16.     | <i>C</i> <sub>2</sub> | 0.01µF         | 0.005 µF     | 1.00e <sup>+03</sup>  | N      |

Table: 1 Result for Biquadratic Filter Circuit.

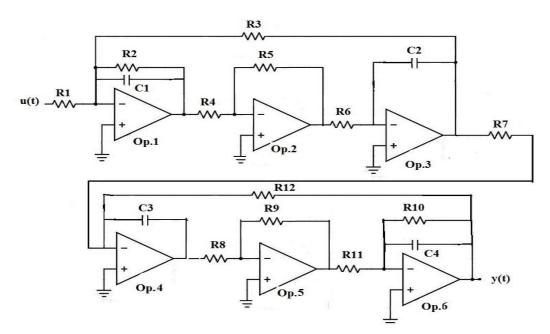

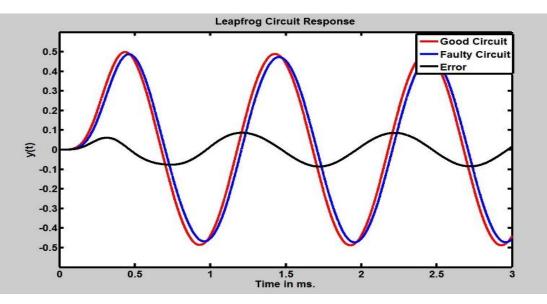

Second leapfrog filter is simulated with the help of our approach by assuming the fault in  $R_5$  resistor. In this case we also assume the parametric fault in circuit. And by simulation of algorithm at 1 KHz, we detect fault in circuit. Fig. 9 shows circuit diagram for leapfrog circuit and fig. 10 shows fault simulation result for leapfrog circuit.

Figure 10: Leapfrog circuit diagram.

Figure 11: Response of Leapfrog Filter Circuit at f= 1000Hz.

#### CONCLUSION

We proposed a new approach for fault detection in linear analog VLSI circuit. This approach is done by discretizing the circuit in z domain and sampling frequency is chosen such that we get maximum accuracy. In this paper all the simulation and calculation for transfer function ,state equation in s domain as well as z domain are done with the help of MATLAB and all model for algorithm are construct with the help of SIMULINK. This approach is very effective to linear analog VLSI and our proposed algorithm is applicable to mostly all analog VLSI circuit.

#### REFERENCES

- L. Milor and A.L. Sangiovanni-Vincentelli, "Minimizing ProductionTest Time to Detect Faults in Analog Circuits," IEEETrans. on Computer-Aided Design, June 1994; 13: 796–813.

- 2. N.B. Hamida and B. Kaminska, "Multiple Fault Analog Circuit Testing by Sensitivity Analysis," J. Electronic Testing: Theory and Applications, 1993; 4: 331–343.

- K. Maggard, P. Karunaratna, C. Stroud, "Built-InSelf Test for analog circuits in Mixed Signal System," Proc.IEEE Southeast Regional Conf., 1999.

- 4. A. Chatterjee. Concurrent Error Detection in Linear Analog and switched-capacitor state variable systems using continuous checksums. Pmc IEEE Intl. Test ConI, 1991; 582-591.

- 5. M.E. Van Valkenburg. Analog Filter Design. Holt, Rinehart and Winston, 1982.

- 6. Seshu, Balabanian. Linear Network Analysis. John Wiley, 1959.

- A. Chatterjee. Checksum-based Concurrent Error Detection in Linear Analog Systems with second and higherorders. Pmc IEEE VLSI Test Symp, 1992; 286-291.

- Luo, Hui, Youren Wang, and Jiang Cui. "A SVDD approach of fuzzy classification for analog circuit fault diagnosis with FWT as preprocessor."Expert Systems with Applications, 2011; 38(8): 10554-10561.

- Vineela, J., G. Praneetha, R. Harshad, K. Masrunnisa, M. Pruthvi Kumar, and T. Sandeep. "A Complete Analysis of Tolerance of Component in Analog VLSI Circuits Using Sensitivity, 2016.

- N. Balabanian, T.A. Bickart, and S. Seshu, Electrical Network Theory, John Wiley & Sons, Inc, 1969.

- 11. Yuan, Lifen, Yigang He, Jiaoying Huang, and Yichuang Sun. "A new neural-networkbased fault diagnosis approach for analog circuits by using kurtosis and entropy as a preprocessor." IEEE Transactions on Instrumentation and Measurement, 2010; 59(3) 586-595.

- 12. The MathWorks Inc. MATLAB User's Guide, 2012.

- 13. Yang, Chenglin, Shulin Tian, Bing Long, and Fang Chen. "Methods of handling the tolerance and test-point selection problem for analog-circuit fault diagnosis." IEEE Transactions on Instrumentation and Measurement, 2011; 60(1): 176-185.

- 14. B. Kaminska, K. Arabi, I. Bell, P. Goteti, J. L. Heurtas, B. Kim, A. Rueda, and M. Soma" Analogand Mixed-Signal Benchmark Circuits First Release", IEEE International Test Conference, Washington DC, November 1997.

- 15. Lin, Tsung-Chih. "Analog circuit fault diagnosis under parameter variations based on type-2 fuzzy logic systems." International Journal of Innovative Computing, Information and Control, 2010; 6(5): 2137-2158.

- 16. A. Meixnerand W. Maly, "Fault Modelingforthe Testing of Mixed Integrated Circuits, "Proc. Of the IEEE Int' 1.Test Conf., Oct., 1991; 564–572.

- 17. Cui, Jiang, and Youren Wang. "A novel approach of analog circuit fault diagnosis using support vector machines classifier." Measurement, 2011; 44(1): 281-289.

- Vasan, Arvind Sai Sarathi, Bing Long, and Michael Pecht. "Diagnostics and prognostics method for analog electronic circuits." IEEE Transactions on Industrial Electronics, 2013; 60(11): 5277-5291.

- 19. Van de Plassche, Rudy J. CMOS integrated analog-to-digital and digital-to-analog converters. Vol. 742. Springer Science & Business Media, 2013.

- 20. Osseiran, Adam, ed. Analog and mixed-signal boundary-scan: A guide to the IEEE 1149.4 test standard. Vol. 16. Springer Science & Business Media, 2013.